本記事は,アナログ・デジタル変換器(ADC)を題材に,筆者自身の理解を深める目的で整理している「ADC入門シリーズ」の一部です.シリーズ全体の方針や位置づけについては,以下の記事をご覧ください.

はじめに

前回までの記事では,スイッチトキャパシタについて学習し,アンプや積分器の回路について整理しました.これまで扱ってきたスイッチトキャパシタ(SC)アンプや積分器では,オペアンプは理想的な特性を持つものとして仮定してきました.

しかし実際の回路では,オペアンプには様々な非理想性が存在します.DC オフセットや有限利得といった非理想性は実装上必然的に現れるものであり,高精度な回路設計においては無視することができません.

本記事では,まずこれらの非理想性の要因について簡単に整理し,その後,SC アンプおよび SC 積分器における補正方法について,基本的な考え方から丁寧に解説していきます.

非理想性の補正手法には様々なものがありますが,本シリーズでは代表的な手法を取り上げ,段階的に理解していきます.ボリュームがあるため,全3回に分けて解説する予定です.

スイッチトキャパシタアンプの非理想性

SC アンプにおける主な非理想性を整理します.

DCオフセット

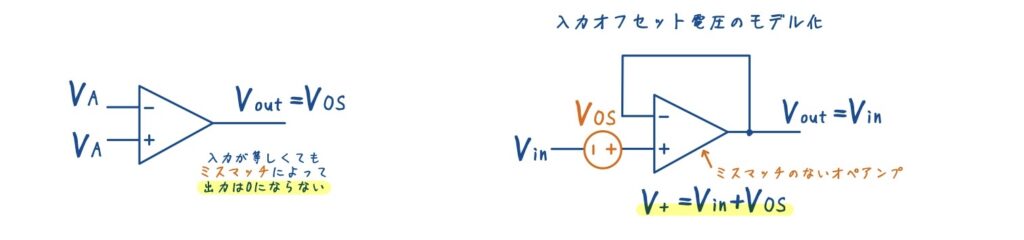

トランジスタのミスマッチにより,オペアンプには入力オフセット電圧が生じます.オペアンプの入力段は一般に差動対で構成されており,理想的には左右のトランジスタは完全に一致している必要があります.しかし実際にはプロセスばらつきにより,それぞれのトランジスタの閾値電圧 \(V_{th}\) やトランスコンダクタンスがわずかに異なります.その結果,両入力に同じ電圧を与えた場合でも,差動対の電流に不均衡が生じ,出力にオフセットが現れます.このとき,この不均衡を打ち消すために必要な入力電圧として定義されるのが入力オフセット電圧です.

解析においては,このオフセットを等価的に \(V_{OS}\) という電圧源としてモデル化します.これは,オペアンプの入力に直列に電圧源が存在するものとして扱うことで,回路全体への影響を簡潔に表現するためのものです.ただし,実際にこのような電圧源が回路内に存在するわけではなく,あくまで解析上の等価モデルである点に注意が必要です.

1/fノイズ(フリッカーノイズ)

トランジスタには,周波数に反比例して増加するフリッカーノイズ(1/fノイズ)と呼ばれる雑音成分が存在します.そのパワースペクトル密度は下式で表され,周波数が低くなるほどノイズ成分が大きくなる特徴を持ちます.特にDC付近ではこのノイズが支配的となります.

\(S(f) \propto \frac{1}{f}\)

フリッカーノイズは DC 付近で大きく,時間的にもゆっくり変動するため,短時間で観測すると一定のオフセットのように見えるという性質があります.このため実際の回路解析や設計では,DC オフセットと同様のものとして扱うこともあります.

発生要因としては,トランジスタ内部におけるキャリアのトラップ・放出などの現象に起因すると考えられていますが,筆者はこのあたりのデバイスメカニズムについてあまり詳しくないため,正しく理解したい場合は「フリッカーノイズ」や「1/f ノイズ」で調べると詳しい解説が得られます.

有限利得(finite gain)

理想的なオペアンプでは \(A \to \infty\) と仮定していましたが,実際のオペアンプの利得は有限です.そのため,出力電圧は

V_{out} = A (V_+ – V_-)

で表され,これを変形すると

V_+ – V_- = \frac{V_{out}}{A}

となります.

理想オペアンプでは \(V_+ = V_-\) が成立(virtual short)していましたが,有限利得の場合は \(V_+ – V_- \neq 0\) のため,オペアンプが入力差を完全にゼロにできないということを意味しています.

DCオフセットの課題

まずは,DCオフセットと1/fノイズの影響について考えます.前節で述べた通り,本記事では1/fノイズもDCオフセットにマージして扱います.DCオフセットおよび1/fノイズによって生じる入力のオフセット電圧を \(V_{OS}\) とし,下図のようにモデル化します.また,要因を切り分けるため,本節では,オペアンプの利得は無限大であると仮定し,まずはオフセットの影響のみを考えます.

SCアンプの理想的な動作は \(V_{out} = \frac{C}{C_F} V_{in}\) でしたが,ここではオフセットが存在する場合の回路動作を考えます.

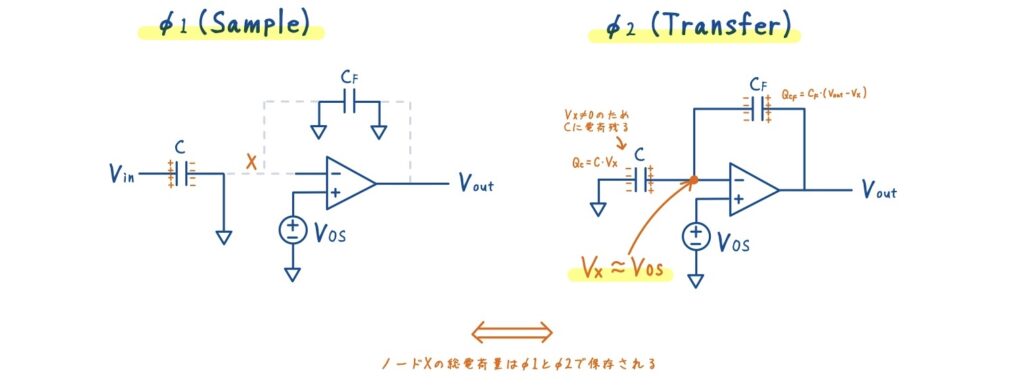

まず,\(\phi_1\) のフェーズではこれまでと同様に,サンプリング容量 \(C\) に入力電圧 \(V_{in}\) が印加され,\(Q_c = C \cdot V_{in}\) の電荷が保持されます.

次に,\(\phi_2\)のフェーズに移ります.入力にオフセット電圧 \(V_{OS}\) が存在するため,ノード \(V_X\) は0ではなく \(V_X = V_{OS}\) となります.理想的には \(V_X = 0\) であるため,サンプリング容量の電荷はすべてフィードバック容量に転送されますが,オフセットが存在する場合はそうなりません.

\(V_X = V_{OS}\) であるため,サンプリング容量には \(C \cdot V_{OS}\) に相当する電荷が残り,電荷転送が不完全になります.

一方,フィードバック容量 \(C_F\) には次式の電荷が蓄えられます.

\(Q_{CF} = (V_{out} – V_X) \cdot C_F\)

ここでノード \(V_X\) に着目すると,\(\phi_1\) と \(\phi_2\) の総電荷量は等しいため,電荷保存則より,次式が成り立ちます.

\(- C \cdot V_{in} = C \cdot V_{OS} + (V_{out} – V_X)\cdot C_F\)

ここで \(V_X = V_{OS}\) を代入すると,

\(V_{out} = \frac{C}{C_F} V_{in} + V_{OS}\left(1+\frac{C}{C_F}\right)\)

となります.この式から分かるように,出力電圧には入力信号とは無関係なオフセット項が生じます.さらに重要なのは,オフセットがゲインとともに増幅されるという点です.そのため,DC 信号や微小信号を扱う高精度回路では,大きな誤差源となります.

基本的な対策の考え方

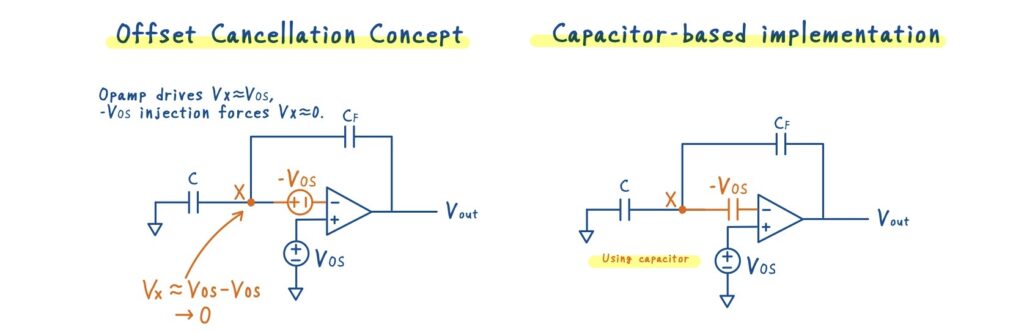

オフセットがある場合,オペアンプは \(V_X = V_{OS}\) となるように動作します.本来,SCアンプでは \(V_X = 0\) (仮想接地)が成立していれば理想的な動作が得られます.したがって,オフセットによる問題は,\(V_X \neq 0\) となることに起因しています.

そのため,解決の基本アイデアは 入力に \(-V_{OS}\) を与える という考え方です.すなわち,オペアンプが作ろうとしているオフセットをあらかじめ打ち消すというアプローチです.これにより,\(V_X = 0\) の状態を再び実現することができます.

\(-V_{OS}\) に相当する電圧源を直接用意することは難しいため,スイッチトキャパシタ回路でよく用いられる 容量による電圧のサンプリング を利用します.容量は一定時間電圧を保持できるため,適切なタイミングで接続することで,\(-V_{OS}\) に相当する電圧を回路内に生成することができます.このようにしてオフセットを打ち消すための容量を,オフセットキャンセル容量 と呼びます.

オフセットキャンセル動作原理

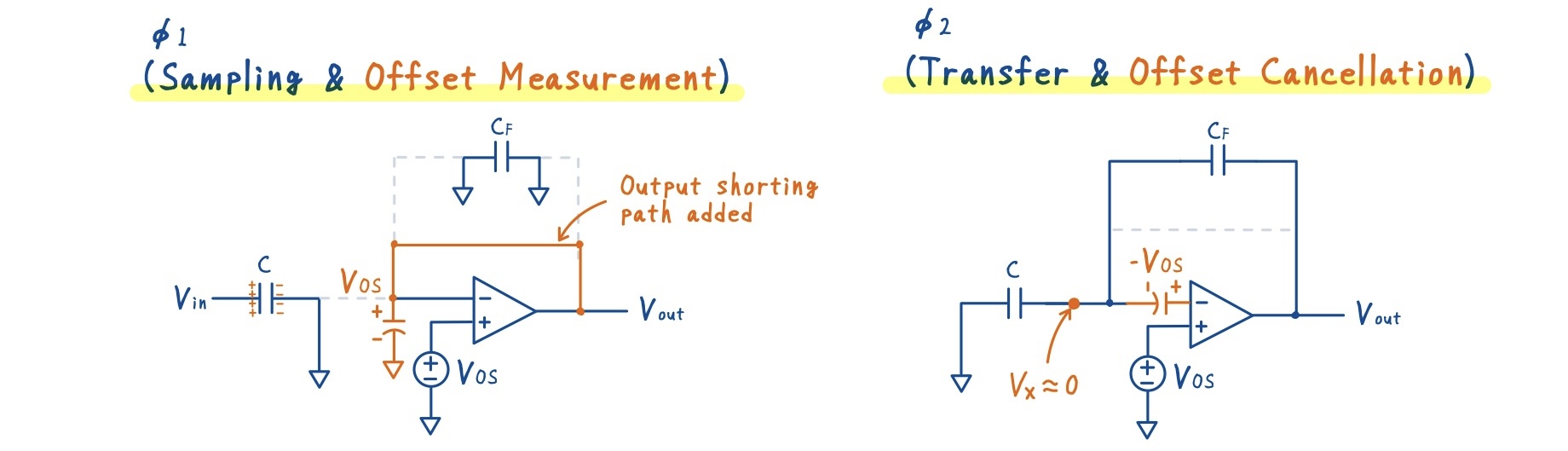

オフセットキャンセルは,2つのクロックフェーズで動作します.重要なのは,オフセットキャンセル容量に,\(\phi_1\)のフェーズで補正電圧をチャージすることです.

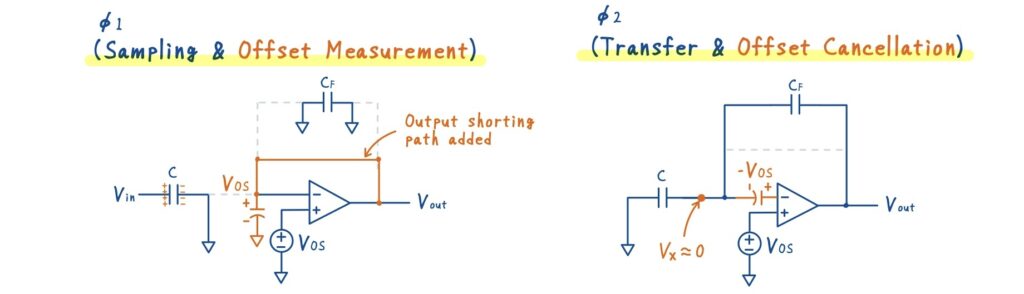

\(\phi_1\):オフセットのサンプリング

まず,入力オフセット電圧 \(V_{OS}\) をオフセットキャンセル容量 \(C_{off}\) にサンプリングします.

ただし,\(V_{OS}\) はあくまで解析上導入した等価モデルであり,実際に独立した電圧源として存在するわけではありません.そのため,単純に「\(V_{OS}\) を直接容量に接続してチャージする」ことはできません.

そこで,オペアンプの性質を利用します.\(\phi_1\)のフェーズでは,下図のようにフィードバックループ経路を短絡することで,オペアンプの入力差がオフセット電圧に一致するような状態を作ります.このとき,オペアンプの出力は \(V_{out} = V_{OS}\) となります.

この構成により,オフセットキャンセル容量 \(C_{off}\) には \(V_{OS}\) に相当する電圧がサンプリングされます.

\(\phi_2\):補正の適用

次に,\(\phi_2\)のフェーズでは,オフセットキャンセル容量 \(C_{off}\) を回路に接続します.このとき,\(\phi_1\)でサンプリングされた電圧 \(V_{OS}\) が,接続の極性により \(- V_{OS}\) として入力側に加えられます.

同時に,\(\phi_1\)で短絡していたフィードバック経路は元に戻し,通常のフィードバック容量 C_F を用いた構成に復帰します.

\(\phi_2\)では,オペアンプはもともと \(V_X = V_{OS}\) となるように動作しようとしますが,入力側に \(-V_{OS}\) が加えられることで,

\(V_X = V_{OS} + (-V_{OS}) = 0\)

となり,仮想接地が再び成立します.その結果,ノード \(V_X\) は理想と同様に0となり,電荷転送が完全に行われます.すなわち,\(\phi_1\)でサンプリングされた電荷 \(Q_c = C \cdot V_{in}\) はすべてフィードバック容量 \(C_F\) に転送され,サンプリング容量 \(C\) に電荷は残りません.

以上の動作から,出力電圧にはオフセットに起因する項は現れず,オフセットをキャンセルできた ということになります.

有限利得の場合の課題

前章までの説明で,入力オフセットによる誤差は完全に解決できるように思えたかもしれませんが,実際にはそう上手くはいきません.残念ながらここまでの議論は,オペアンプの利得が無限大であることを仮定していました.実際には利得は有限となるので,完全なオフセットキャンセルには至りません.

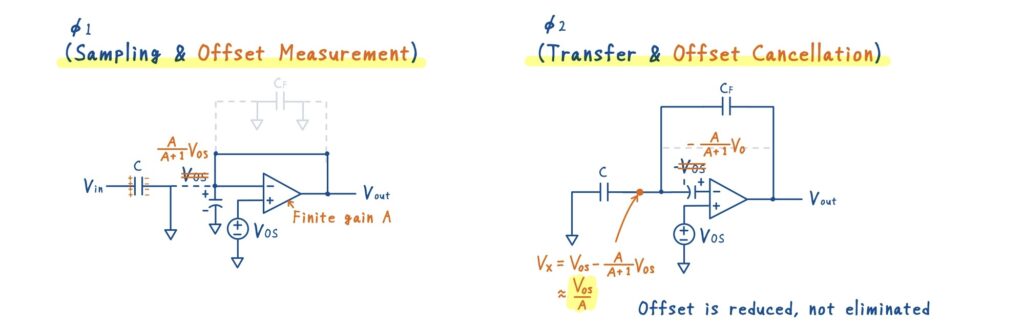

オペアンプの利得を有限値 \(A\) とすると,\(\phi_1\)のフェーズはユニティゲインのフィードバック構成となるため,出力電圧は次式になります.

\(V_{out} = \frac{A}{A+1}V_{OS}\)

したがって,オフセットキャンセル容量にサンプリングされる電圧も,\(\frac{A}{A+1} V_{OS}\) となります.

この状態で\(\phi_2\)のフェーズに移ると,ノード \(V_X\) の電圧は

\(V_X = V_{OS} – \frac{A}{A+1} V_{OS}\)

となり,整理すると

\(V_X = \frac{V_{OS}}{A+1} \approx \frac{V_{OS}}{A}\)

となります.このように,オフセットは完全には打ち消されず,\(\frac{1}{A}\) 倍に縮小されるにとどまります.したがって,オペアンプの利得 A が大きいほど,オフセット誤差は小さくなります.一方で,利得を高くするには回路規模や消費電力の増加を伴うため,必要な精度に応じて利得を適切に設計することが重要となります.

このように,本手法によってオフセットを低減することは可能ですが,有限利得による残留誤差が存在するため,さらなる高精度化には別の手法が必要となります.

まとめ

本稿では,SC アンプにおける非理想性と,その基本的な補正方法について整理しました.

ポイントを振り返ると,次のとおりです:

- オペアンプには,DC オフセット,1/f ノイズ,有限利得といった非理想性が存在する.

- DC オフセットおよび 1/f ノイズは,入力オフセット電圧 \(V_{OS}\) として等価的にモデル化できる.

- SC アンプでは,ノード \(V_X = 0\)(仮想接地)が成立することが理想動作の前提となる.

- オフセットが存在する場合,\(V_X \neq 0\) となり,電荷転送が不完全になる.

- 補正容量を用いることで,\(-V_{OS}\) を入力側に与え,オフセットを打ち消すことができる.

- 有限利得の影響により,オフセットは完全には除去されず,\(\frac{1}{A}\) 倍に縮小されるにとどまる.

今回扱ったオフセットキャンセルは,スイッチトキャパシタ回路における最も基本的な補正手法の一つです.しかし,有限利得による残留誤差や,より高精度な回路設計を考えると,この手法だけでは十分ではありません.

次回は,これらの課題をさらに改善する手法である Correlated Double Sampling(CDS) について解説します.オフセットや 1/f ノイズをどのようにして抑制するのか,本記事で整理した「\(V_X = 0\) を実現する」という視点を軸に見ていくことで,理解がより深まるはずです.

以上です.最後まで読んでいただきありがとうございました.

参考文献

本記事はあくまで筆者の勉強備忘録のため,より正確に理解したい,さらに深く理解したい場合は下記をご参照ください.

- IIT Kanpur: https://www.iitk.ac.in

- SSCD Lab: https://iitk.ac.in/sscd

- 講義動画(YouTube): https://youtu.be/cI7bYpW7EvE?si=uhuL8tSMJan23LHf

- 『アナログ/デジタル変換入門 ― 原理と回路実装 ―』 和保孝夫(監)/コロナ社

- 『ΔΣ型アナログ/デジタル変換器入門 第2版』 和保孝夫・安田彰(監訳)/丸善出版

- 『アナログCMOS集積回路の設計 応用編』Behzad Razavi(著),黒田忠弘(監訳)/丸善出版

ー 第12章 スイッチトキャパシタ回路 ー - 『CMOSアナログ回路入門』 谷口研二(著)/CQ出版社

ー 第15章 スイッチト・キャパシタ ー

(ADCの基礎を一通り確認する目的で,最初の一冊として取り組みやすい内容です.)

(筆者が所持しているのは第 1 版ですが,こちらも分かりやすくておすすめです.)

スイッチトキャパシタについては,下記2冊が分かりやすいです.