本記事は,アナログ・デジタル変換器(ADC)を題材に,筆者自身の理解を深める目的で整理している「ADC入門シリーズ」の一部です.シリーズ全体の方針や位置づけについては,以下の記事をご覧ください.

はじめに

前回の記事では,SC積分器(Switched Capacitor Integrator)の動作原理を整理し,遅延付きと遅延なしの構成の違いを,伝達関数 \(H(z)\) と回路動作の両面から確認しました.

今回は一歩進めて,与えられた伝達関数から回路構成を導くという設計演習を行います.一見複雑に見える伝達関数も,基礎要素に分解することができれば,設計も難しくはありません.伝達関数の数式と回路図のイメージを往復できることを目標に,本稿では一つずつ丁寧に整理していきます.

演習テーマ

本稿では,参考動画内で扱われていた演習問題を題材に,その内容をより深く掘り下げて解説していきます.本稿で扱う伝達関数は次式とします.

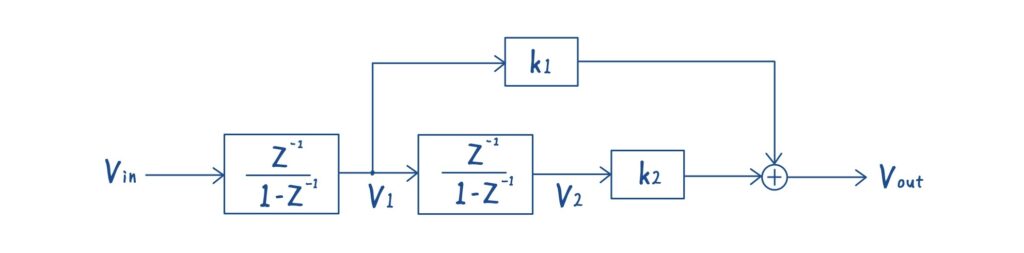

\(H(z) = k_1 \frac{z^{-1}}{1 – z^{-1}} + k_2 \left( \frac{z^{-1}}{1 – z^{-1}} \right)^2\)

この伝達関数を実現するスイッチトキャパシタ回路を,段階的に構成していきます.一見すると複雑に見えますが,構造を分解していくと,遅延付き積分器の組み合わせであることが分かります.つまり,本質的にはこれまで学んできた基本ブロックの線形結合に過ぎません.

なお,本稿で扱う構造は,ΔΣADCやスイッチトキャパシタフィルタに頻出する典型的な形式です.その内部構造を理解することは,離散時間回路の理解に直結します.

以下の手順で回路を構成していきます.

- 1次の遅延付き積分器の構成

- カスケード接続による2次遅延付き積分器

- スケーリング係数 \(k_1, k_2\) の決定

- 出力加算回路の構成

1.1次の遅延付き積分器

まずは初項について考えます.

\(\frac{z^{-1}}{1 – z^{-1}}\)

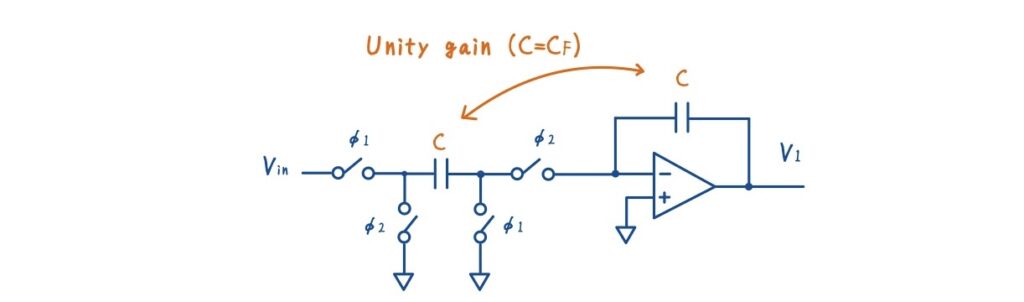

これは前回整理した「遅延付き SC 積分器」の伝達関数です.一般に,遅延付きSC積分器の伝達関数は次式で表されます.

\(H(z) = \frac{C}{C_F} \frac{z^{-1}}{1 – z^{-1}}\)

スケーリング係数 \(k_1\) については後の章で扱うため,ここでは \(C = C_F = C\) とし,容量比(ゲイン)を1と仮定します.したがって,伝達関数は次式となり,演習テーマの伝達関数の初項と一致することが確認できます.

\(V_1(z) = \frac{z^{-1}}{1 – z^{-1}} V_{in}(z)\)

これまでの記事で学んだように,\(\phi_1\)で入力をサンプリングし,\(\phi_2\)で電荷をフィードバック容量へ転送することで,その結果が次の周期まで保持されるという振る舞いです.この「1クロック分の状態更新遅れ」が分子の \(z^{-1}\) に対応します.

2.2次の積分器

次に,第2項に現れる2乗の項について考えます.

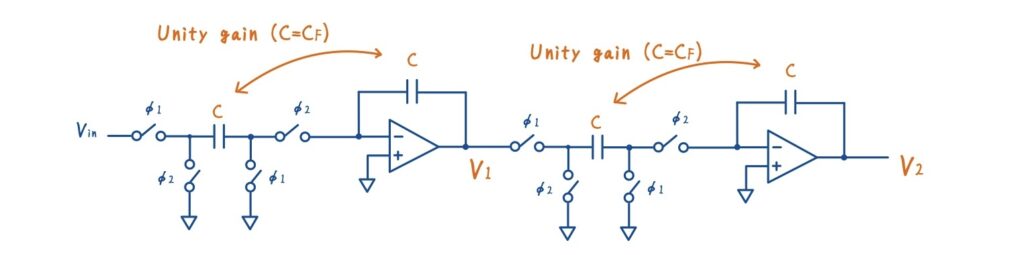

\(\left(\frac{z^{-1}}{1 – z^{-1}}\right)^2\)

これは,遅延付き積分器をもう一段カスケード接続することで実現できます.ここでもスケーリング係数 \(k_2\) は次章で扱うため,本章では \(C = C_F\) とし,容量比を1と仮定します.

1段目の出力を \(V_1\) とすると,2段目の出力 \(V_2\) は次式になります.

\(V_2(z) = \frac{z^{-1}}{1 – z^{-1}} V_1(z)\)

ここで,前節で求めた

V_1(z) = \frac{z^{-1}}{1 – z^{-1}} V_{in}(z)

を代入すると,演習テーマの伝達関数 第 2 項と一致することが確認できます.

\(V_2(z) = \left(\frac{z^{-1}}{1 – z^{-1}}\right)^2 V_{in}(z)\)

以上より,第2項の構造は「遅延付き積分器を2段カスケード接続したもの」であることが分かりました.

3.スケーリング係数 \(k_1,k_2\) の実装方法

次に考えるべきは,係数 \(k_1,k_2\) の実装方法です.スケーリングの方法としては,大きく2通りが考えられます.

各段で容量比を変更する方法

まず思いつくのは,各積分器段で容量比を変更する方法です.例えば \(k_1 = 2\) としたい場合,\(\frac{C}{C_F} = 2\) となるように \(C = 2C_F\) と設計すれば実現できます.しかしこの方法では,1段目のゲイン変更が後段の動作にも影響します.2段目の入力は \(V_1\) であるため,1段目のスケーリングはそのまま2段目の出力にも反映されます.その結果,最終的な出力における \(k_2\) の寄与も間接的に変化します.つまり,\(k_1\) を変更すると,出力全体に対する \(k_2\) の実効的な重みも同時に変化する可能性があります.

このように設計パラメータが独立でなくなると,調整すべき容量が増え,設計自由度が下がります.この観点から,本構成はあまり推奨されません.

分岐後にスケーリングする方法

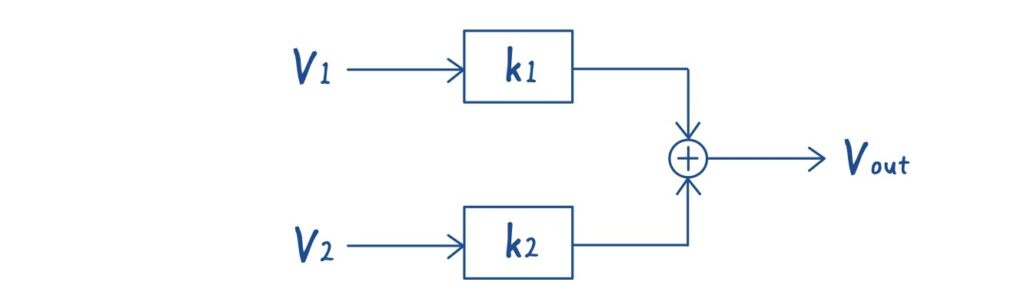

より合理的なスケーリング方法は,積分器と係数調整の役割を明確に分離する構成です.ここではあえて,積分器は容量比1で設計し,スケーリングは後段のブロックで実装します.

まず1段目で \(V_1\) を生成し,さらにその出力を2段目へ渡して \(V_2\) を生成します.この時点で,\(V_1,\quad V_2\) はそれぞれ所望の「状態変数」を表しています.

これらの状態を分岐させ,最終段で係数を掛けることで重み付けを行います.

\(V_{out} = k_1 V_1 + k_2 V_2\)

この構成の利点は,各係数 \(k_1,k_2\) を独立に設計できるため,ある係数を変更しても他の状態生成ブロックに影響を与えません.この考え方は離散時間回路を設計する上での基本思想にもなります.

分岐パスの生成および加算方法については,次章で具体的に扱います.

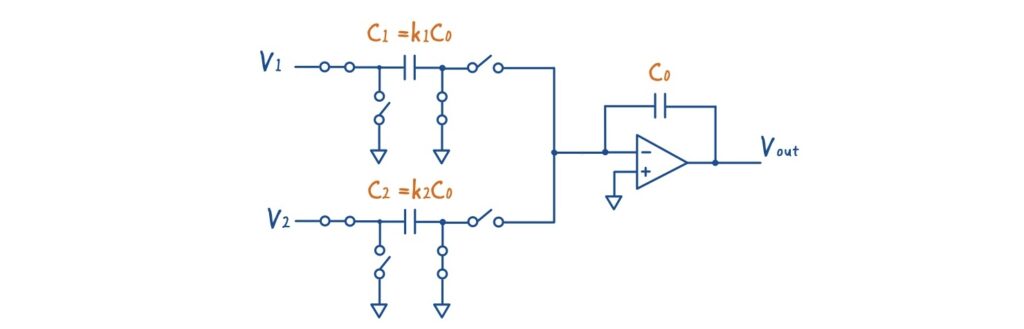

4.スケーリング+加算回路

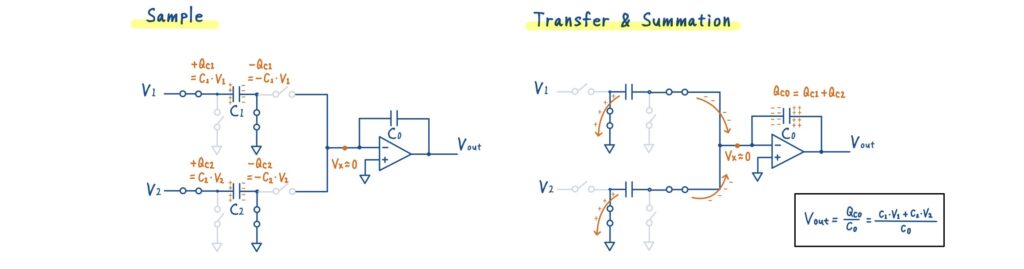

スイッチトキャパシタ回路は,電荷を扱うという点で加算処理と非常に相性がよい構造です.所望のノードへ電荷を転送し,その総和をとるだけで,加算が自然に実現できます.ここでは,前章までで得られた状態変数 \(V_1,\quad V_2\) を入力とし,それらを重み付きで加算する回路を考えます.

まず,各入力をそれぞれのサンプリング容量に取り込みます.

\(Q_{c1} = C_1 V_1\)

\(Q_{c2} = C_2 V_2\)

次に,これらの電荷を同一の仮想接地ノードへ転送します.オペアンプ入力電流は理想的に0であるため,流入した電荷はすべてフィードバック容量 \(C_0\)に現れます.

したがって,フィードバック容量に蓄積される電荷は次式となります.

\(Q_{C0} = Q_{c1} + Q_{c2} = C_1 V_1 + C_2 V_2\)

ここでフィードバック容量 \(C_0\) に対して,各分岐のサンプリング容量を \(C_1 = k_1 C_0,\quad C_2 = k_2 C_0\) と設定します.

すると,\(Q_{C0}\)は次式に置き換えることができます.

\(Q_{CF} = k_1 C_0 V_1 + k_2 C_0 V_2\)

上式を出力電圧へ換算すると,

\(V_{out} = \frac{Q_{CF}}{C_0} = \frac{k_1 C_0 V_1 + k_2 C_0 V_2}{C_0} = k_1 V_1 + k_2 V_2\)

となり,所望のスケーリングと加算が実現できていることが分かります.積分器で生成した状態を取り出し,後段で重み付けして足し合わせることで,伝達関数の構造が回路として具体化しました.

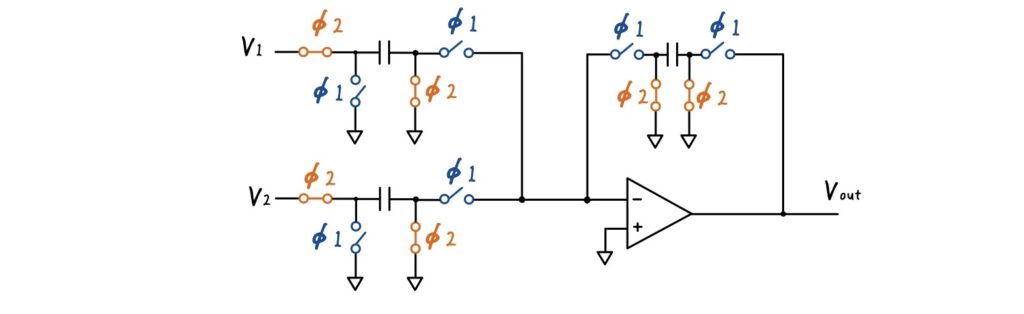

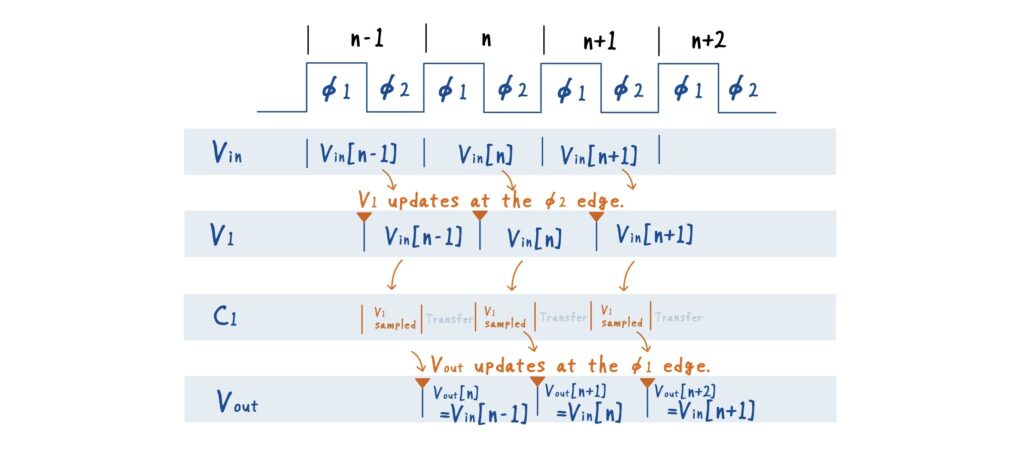

スイッチの開閉順序

スイッチの開閉順序については一工夫が必要です.理由としては,余分な遅延がついてしまうことを避けるためです.この加算回路では,新たな遅延 \(z^{-1}\) を発生させないことが設計上のポイントになります.

分岐後のサンプリング容量は,前段の積分器の順序とは異なり,次の順序にします.

- \(\phi_2\):サンプリング

- \(\phi_1\):フィードバック容量へ転送

このタイミングチャートを下記にに示します.このタイミングチャートを見て分かるように,\(\phi_2\)でサンプリングすることで,状態 \(V_1\) や \(V_2\) が確定した直後の値を取り込むことができます.そのため,出力までの遅延は半クロック分で済み,新たな \(z^{-1}\) は発生しません.一方,\(\phi_1\)でサンプリングしてしまうと,次の周期まで待つ必要が生じます.その結果,状態と出力の間に1クロックの遅延が入り,意図しない \(z^{-1}\) が追加されます.

この違いは見た目以上に重要で,タイミングを誤ると,伝達関数そのものが変わってしまいます.ここでは分かりやすさのために \(V_1\) の分岐路でタイミングを示しましたが,\(V_2\) 側も同様に \(\phi_2\)サンプリング,\(\phi_1\)転送とします.

フィードバック容量のリセット

最終段ではフィードバック容量を毎周期リセットします.これを行わないと,フィードバック容量に電荷が蓄積し続け,回路は積分器として動作してしまいます.本章で実現したいのは「単純な加算」であり,状態の保持ではありません.リセットを行うことで,前サイクルの電荷は解放され,各周期ごとに独立した電荷加算が行われます.

回路図だけを見ると似た構造に見えるかもしれませんが,

- リセットあり → 加算回路

- リセットなし → 積分器

という明確な違いがあります.この区別を曖昧にすると,伝達関数の読み取りを誤ります.SC 回路では,スイッチ1つで回路の意味が変わってしまうので注意です.

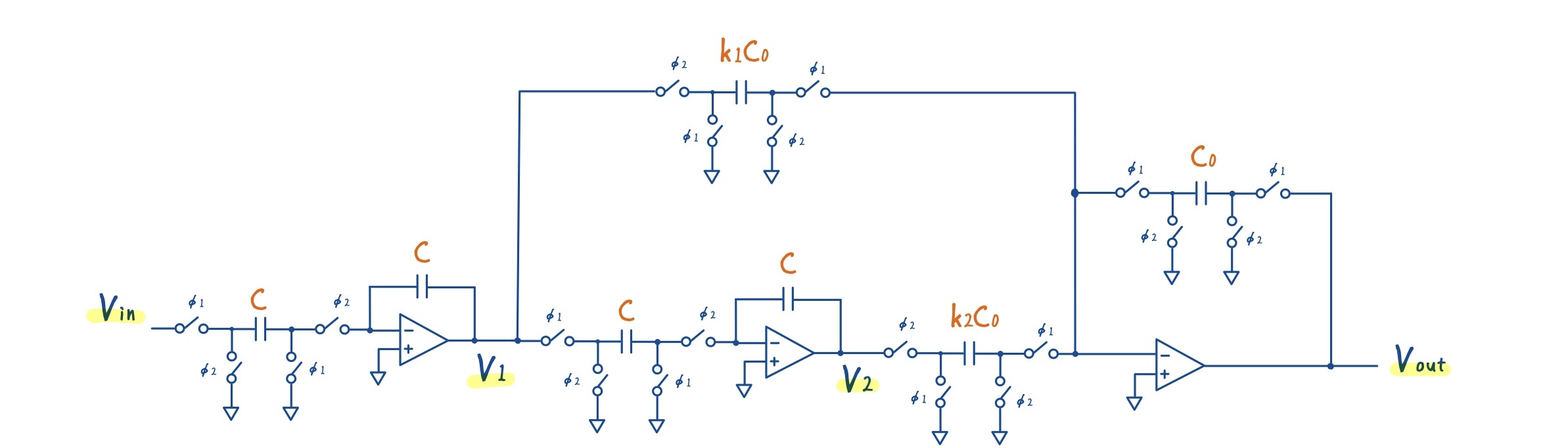

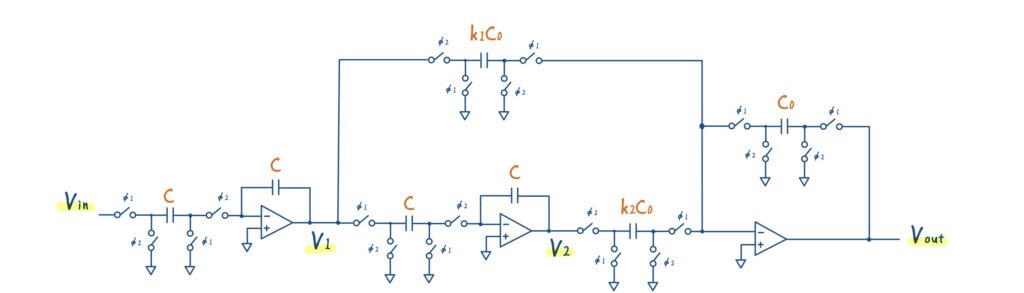

出来上がった回路の確認

改めて,出来上がった回路全体を確認すると下図のようになりました.回路図を見る限りボリュームがありますが,これを z 領域のブロック図にするとよりシンプルな構成になります.z領域のブロック図にすることで,積分器 × 2,重み付け(スケーリング),加算と各回路の役割が明確になっていることが分かります.

このように,回路図と z 領域ブロック図でイメージを往復できることになると,ADC 回路について1段理解が深まってくると思います.

なお,ここまでの議論では理想アンプ・理想スイッチを仮定しており,各ノードは瞬時に所望の電位へ到達するものとして扱っています.しかし,実際の回路では,分岐が増えることで前段ノードの負荷容量が増大し,セトリング時間が悪化する点に注意が必要です.

例えば,本構成では \(V_1\) ノードから複数のサンプリング容量へ電荷を供給しています.そのため,有効負荷容量は増加し,アンプの出力抵抗との積で決まる時定数が大きくなります.結果として,\(\phi_1,\phi_2\) の有効時間内に十分なセトリングが得られない可能性があります.設計段階では,負荷容量の増加がループ帯域や安定性に与える影響を必ず評価し,必要に応じてアンプの \(g_m\) 増強やクロック期間の最適化を検討する必要があります.

まとめ

本稿では,与えられた伝達関数を出発点とし,その回路実装までを一貫して整理しました.

\(H(z) = k_1 \frac{z^{-1}}{1 – z^{-1}} + k_2 \left( \frac{z^{-1}}{1 – z^{-1}} \right)^2\)

ポイントを振り返ると,次のとおりです:

- 初項は遅延付き SC 積分器

- 第2項(2乗項)は,積分器をカスケード接続することで実現できる.

- 積分器にはゲインを持たせず,状態生成に専念させることで設計パラメータを独立に保てる.

- 係数 k_1, k_2 は分岐後のサンプリング容量比によって実装できる.

- SC 回路では電荷保存則により自然に加算が実現できる.

- スイッチのタイミングを誤ると,新たな \(z^{-1}\) が発生し,伝達関数が変化する.

今回扱った構成は特別なものではなく,ΔΣ ADC や SC フィルタで頻出する基本回路です.伝達関数から回路へ,回路から再び z 領域へと往復できるようになると,離散時間回路の見え方が一段深まるはずです.今後より複雑な構成が登場しても,本記事で整理したように,基本要素に分解して考えることで,回路図から伝達関数を読み取る力が養われると思います.

以上です.最後まで読んでいただきありがとうございました.

雑記:まもなくADC入門シリーズが20本目の記事を迎えます.ようやく半分くらいまできたかなという感触です.

記事を書くことにはだいぶ慣れてきましたが,MathJaxは今でもよく誤記をしてしまいます.

修正が必要な箇所を見つけられましたら,お気軽に教えていただけますと幸いです.引き続きよろしくお願いいたします.

参考文献

本記事はあくまで筆者の勉強備忘録のため,より正確に理解したい,さらに深く理解したい場合は下記をご参照ください.

- IIT Kanpur: https://www.iitk.ac.in

- SSCD Lab: https://iitk.ac.in/sscd

- 講義動画(YouTube): https://youtu.be/cI7bYpW7EvE?si=uhuL8tSMJan23LHf

- 『アナログ/デジタル変換入門 ― 原理と回路実装 ―』 和保孝夫(監)/コロナ社

- 『ΔΣ型アナログ/デジタル変換器入門 第2版』 和保孝夫・安田彰(監訳)/丸善出版

- 『アナログCMOS集積回路の設計 応用編』Behzad Razavi(著),黒田忠弘(監訳)/丸善出版

ー 第12章 スイッチトキャパシタ回路 ー - 『CMOSアナログ回路入門』 谷口研二(著)/CQ出版社

ー 第15章 スイッチト・キャパシタ ー

(ADCの基礎を一通り確認する目的で,最初の一冊として取り組みやすい内容です.)

(筆者が所持しているのは第 1 版ですが,こちらも分かりやすくておすすめです.)

スイッチトキャパシタについては,下記2冊が分かりやすいです.