本記事は,アナログ・デジタル変換器(ADC)を題材に,筆者自身の理解を深める目的で整理している「ADC入門シリーズ」の一部です.シリーズ全体の方針や位置づけについては,以下の記事をご覧ください.

はじめに

前回の記事では,Z 変換について学び,差分方程式を Z 変換によって伝達関数へ変換する方法を整理しました. \(z^{-1}\) が1サンプル遅延を意味することを確認し,スイッチトキャパシタアンプの伝達関数 \(H(z)\) の導出まで行いました.

今回扱うのは,ADC設計における最重要ブロックの一つである積分器です.ΔΣ型変調器やパイプライン ADC など,いずれの回路でも主役級の働きをする積分器の理解は避けて通れません.

本稿では,積分回路の基礎を押さえたのち,伝達関数 \(H(z)\) の導出とスイッチトキャパシタ回路による実装までを整理していきます.理論と回路が明確につながるよう意識してまとめましたので,一緒に学んでいきましょう.

連続時間での積分器

そもそも積分器とは,その名の通り,入力信号を積分(蓄積)して出力する回路です.

時間領域では,

\(y(t) = \int_{0}^{t} x(\tau)\, d\tau\)

と表すことができ,ある区間の入力を蓄積し続けることが分かります.また,理想的な連続時間積分器の伝達関数をラプラス領域で示すと,

\(H(s) = \frac{1}{s}\)

となります.

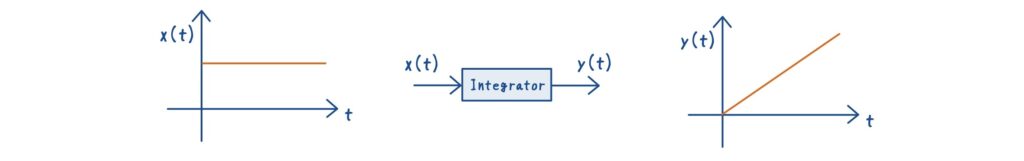

例えば,下図のように入力が一定であれば,出力は一定値が蓄積され続けるため,ランプ状に増加します.

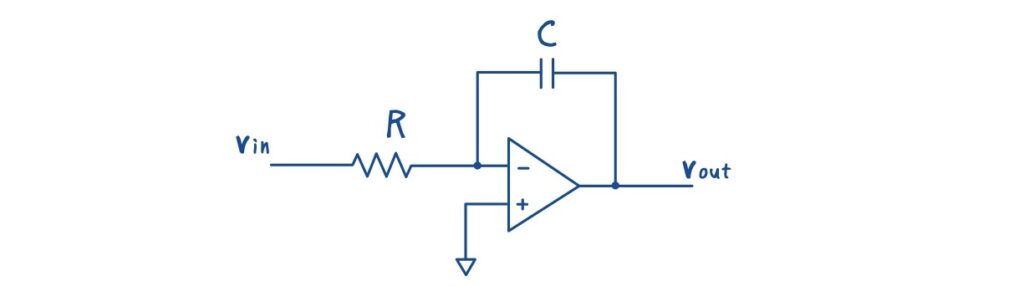

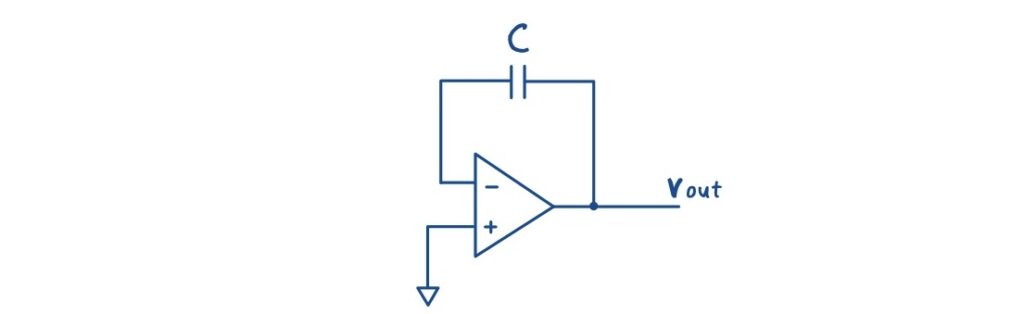

この積分器の基本的な実装は,下図に示すように,オペアンプに抵抗と容量を組み合わせた構成です(入力側に抵抗 \(R\),フィードバックに容量 \(C\)).

この回路の出力電圧は,下式になります.

\(V_{out}(t) = – \frac{1}{RC} \int V_{in}(t)\, dt\)

各パラメータの物理的意味としては,抵抗 \(R\)が入力電圧を電流に変換し,容量 \(C\)が流れ込んだ電流を蓄積します.容量の基本式 \(i = C \frac{dv}{dt}\) を思い出すと,電流を流し続ければ電圧は積分された形で増加していくことが分かります.つまり,容量そのものが「電流を積分して電圧に変換する素子」ということです.

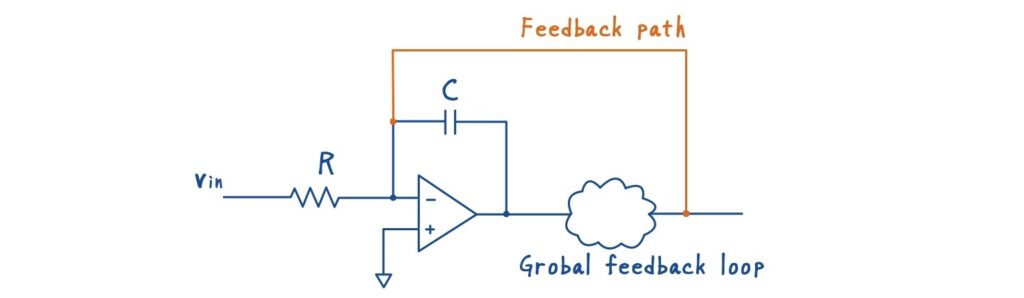

補足として,積分器は単独では使用しません.DC で考えると,容量はオープンとして振る舞うため帰還経路が存在せず,動作点が適切に決まりません.また,わずかなオフセット電圧やバイアス誤差があれば,出力はランプ状に発散し,やがて電源レールへ飽和してしまいます.したがって,積分器は必ず負帰還ループの一部として用いる,というのが実務上の鉄則です.

離散時間での積分器

前章までは,連続時間における積分器について考えました.本章では,離散時間における積分器を解説します.ADC では信号はサンプリングされるため,必然的に離散時間の考え方が必要になります.離散時間信号の場合,積分は総和で表すことができます.

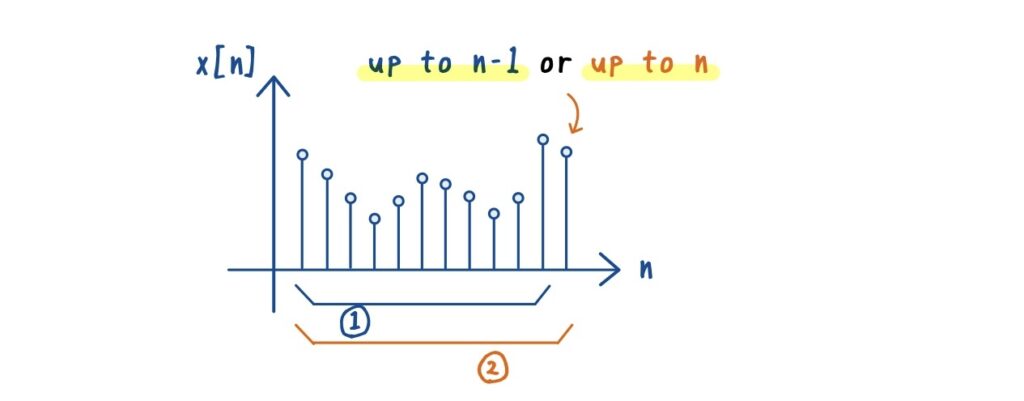

離散時間における積分には定義にわずかな違いがあり,ある時刻における出力を求める方法として,2 通りの総和の取り方が考えられます.下図に示すように,

- ①直前のサンプルまで足し合わせる手法

- ②現在の入力サンプルも含めて足し合わせる手法

の2種類です.それぞれ,①を遅延付き積分器,②を遅延なし積分器と呼ぶこととします.

① 遅延付き積分器

まずは,遅延付き積分器について解説します.こちらは,直前のサンプルまで足し合わせる方法のため,出力値は下記のように定義することができます.

\(y[n] = \sum_{k=0}^{n-1} x[k]\)

また,ここで,ひとつ前の出力値については,下記になります.

\(y[n-1] = \sum_{k=0}^{n-2} x[k]\)

\(y[n-1]\) に \(x[n-1]\)を足し合わせたものが,\(y[n]\) となるので,差分方程式は下記のように求められます.

\(y[n] = y[n-1] + x[n-1]\)

これを前回の記事で学んだZ変換を用いると,下式のように表すことができます.

\(H[z] = \frac{z^{-1}}{1 – z^{-1}}\)

分子に \(z^{-1}\) が含まれていることから分かるように,出力は1サンプル遅れます.このため「遅延付き積分器」と呼ばれます.

② 遅延なし積分器

一方,同様の手順でもう一方の差分方程式を求めると下式になります.①との差分としては\(x[n-1]\) が \(x[n]\) になっている点で,現在の値も総和に含めていることが分かります.

\(y[n] = y[n-1] + x[n]\)

この差分方程式を Z 変換し,\(H(z)\)としてまとめると下式になります.

\(H[z] = \frac{1}{1 – z^{-1}}\)

こちらは分子に \(z^{-1}\) が含まれないため,遅延はありません.

離散時間積分器の回路実装

ここからが本題で,離散時間積分器の回路実装を解説していきます.

これまで学んできた通り,スイッチトキャパシタ回路は離散時間信号処理と非常に相性が良い構成です.したがって,本章では SC 回路を基盤として積分器を実現します.

\(y[n−1]\) の実装

\(y[n−1]\) とは,前回の出力を保持することです.したがって,容量で電荷を保持し,オペアンプで電荷を失わず処理することで構成可能です.

出力を容量 \(C_F\) に保持し,仮想接地点を利用して電荷保存を成立させます.これはすでにスイッチトキャパシタ増幅器で見た考え方と同じです.

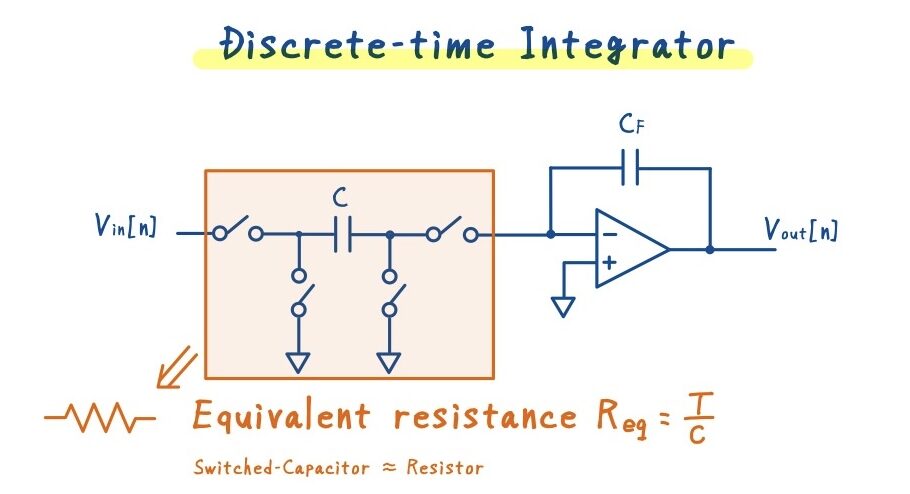

遅延付き積分器

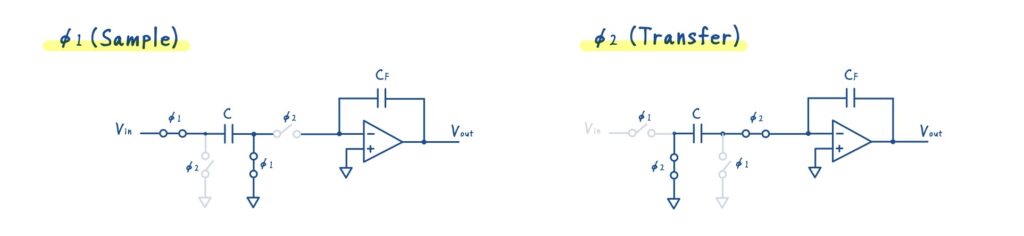

次に,入力のサンプリング値を出力へ加算する回路を考えます.これは,以前の記事で学んだスイッチトキャパシタアンプの構成から「リセット機能」を除いた形で実装できます.

動作概要は次の通りです.

- フェーズ \(\phi_1\) で入力値 \(x[n]\) をサンプリング

- フェーズ \(\phi_2\) で電荷を \(C_F\) に転送

この動作により,差分方程式を Z 変換すると以下の伝達関数が得られます.

\(H[z] = \frac{C}{C_F} \cdot \frac{z^{-1}}{1 – z^{-1}}\)

ゲインは容量比によって決定され,\(k=C/C_F\) となり,正の符号となります.

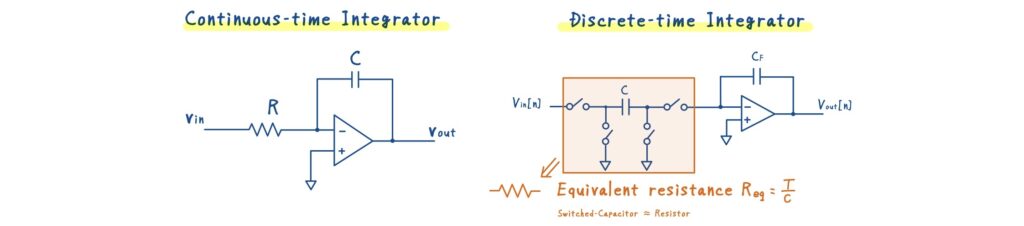

スイッチトキャパシタ回路を考えると,時間平均的に容量は次式のように抵抗と等価になります.したがって,連続時間積分器の RC 構成と対応関係を持ち,SC 回路が離散時間版の抵抗の役割を担っていることが分かります.

\(R_{eq} = \frac{T}{C}\)

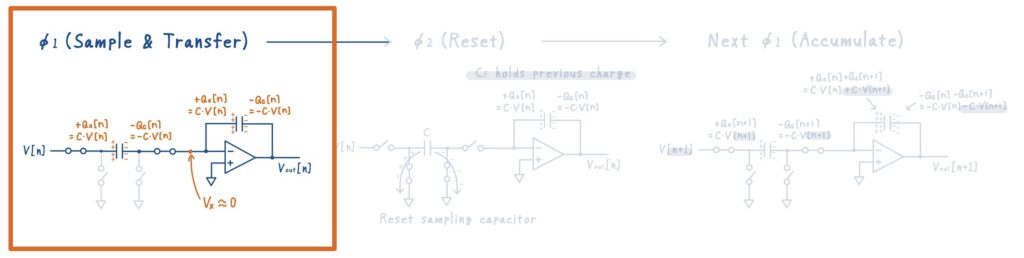

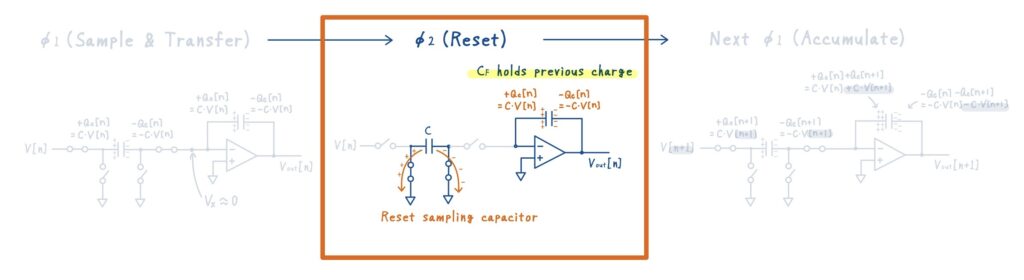

遅延なし SC 積分器

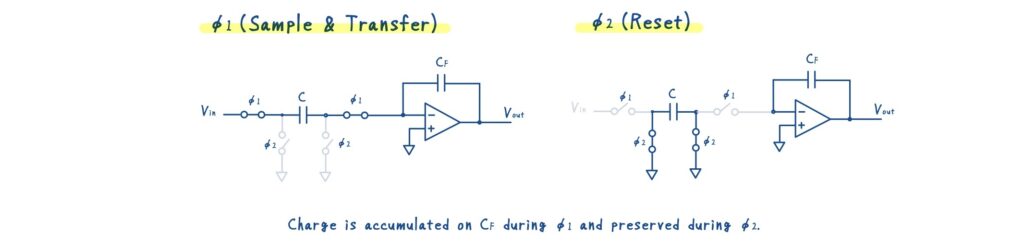

遅延なしの SC 積分器は同一フェーズで,サンプリング・電荷転送・出力取得を行う必要があります.これらの要求は下図のような構成にすることで実現ができます.構成は遅延付き SC 積分器と同様ですが,スイッチの開閉順序が異なりますので,順番に動作概要を解説していきます.

\(\phi_1\)フェーズ(サンプリングと加算)

フェーズ \(\phi_1\) では,入力電圧 \(V[n]\) がサンプリング容量 \(C\) に印加されます.このとき,容量 \(C\) の左側プレート(入力側)には \(Q_C = + C V[n]\) の電荷が生じます.一方,右側プレート(仮想接地点側)は,\(- C V[n]\) の電荷が生じます.

ここで重要なのは,仮想接地点ノードに流れ込む電流はゼロであるため,そのノードの総電荷は保存されるという点です.したがって,サンプリング容量の右側プレートに \(- C V[n]\) が現れたならば,同じノードに接続されているフィードバック容量 \(C_F\) の左側プレートには \(+ C V[n]\)が現れます.(電荷保存則)

すると,フィードバック容量の出力側プレートには \(- C V[n]\) が生じ,出力電圧は負方向へ変化します.

\(\phi_2\) フェーズ(サンプリング容量のリセット)

フェーズ \(\phi_2\) では,サンプリング容量 \(C\) の両端は GND へ接続されます.したがって,容量 \(C\) に保持されていた電荷は消滅します.しかし,フィードバック容量 \(C_F\) に蓄積された電荷は保持されます.

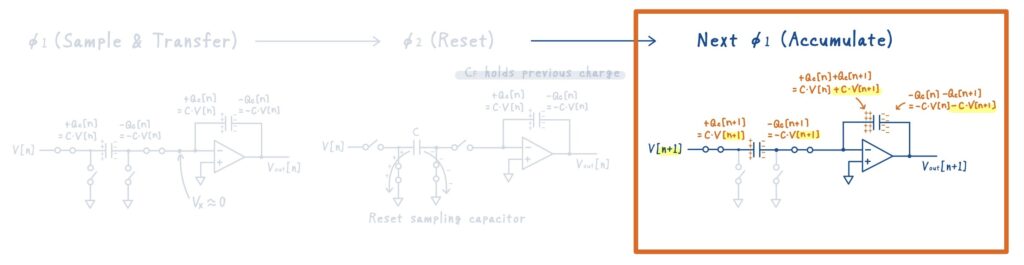

次の \(\phi_1\)

再び入力に比例した電荷がサンプリング容量に蓄積され,同様の電荷保存により \(C_F\) に加算されます.この結果,

\(Q_{C_F}[n] = Q_{C_F}[n-1] + C V[n]\)

となります.

電圧に換算すると,次式になります.

\(V_{out}[n] = V_{out}[n-1] – \frac{C}{C_F} V[n]\)

この差分方程式を解き,\(H(z)=V_{out}(z)/V(z)\) としてまとめると次のようになります.

\(H[z] = \frac{V_{out}[z]}{V[z]} = -\frac{C}{C_F} \cdot \frac{1}{1 – z^{-1}}\)

この式から分かるように,分子に遅延項の \(z^{-1}\) がないため,同一フェーズで,サンプリング・電荷転送・出力取得が可能になります.注意としては,負のゲインを持つため,出力は入力と符号が反転します.

両者の比較

ここまでで,遅延付き積分器および遅延なし積分器について,伝達関数の導出から回路実装までを整理しました.両者の特徴について,改めて比較してみます.

余談ですが,これらの構成はサンプリング容量のスイッチ開閉順序を泳ぎ方に見立てて,①をクロール型,②をバタフライ型と呼ぶことがあります.筆者の知る限り,この呼び方は日本語の文献でのみ見られる表現であり,英語の論文や教科書では一般に「Delay / Delay-free」,あるいは「forward / backward」といった呼称が用いられています.

筆者個人としては,クロール型/バタフライ型という呼び方は動作イメージが直感的で分かりやすいと感じています.本稿では,読者の理解を助ける観点から,この呼称も併用していきます.

| 項目 | ① 遅延付き積分器 | ② 遅延なし積分器 |

|---|---|---|

| 伝達関数 H[z] | \(\displaystyle H[z] = \frac{C}{C_F} \cdot \frac{z^{-1}}{1 – z^{-1}}\) | \(\displaystyle H[z] = -\frac{C}{C_F} \cdot \frac{1}{1 – z^{-1}}\) |

| ゲイン符号 | 正 | 負(反転) |

| 呼称 | Delay integrator Forward 型 クロール型 | Delay-free integrator Backward 型 バタフライ型 |

| タイミング | \(\phi_1\)でサンプリング → \(\phi_2\)で転送 → 次周期で出力確定(1サンプル遅れ) | 同一フェーズ内でサンプリング・転送・出力取得 |

| 特徴 | ・構造が素直で理解しやすい ・出力に1サンプル遅延を含む ・ループ設計時に遅延が明確 | ・遅延が入らない ・ゲインが負になる ・高速ループ設計に有利な場合がある |

これらの違いが正しく理解できるようになると,回路図を見ただけで,伝達関数が直感的にイメージできるようになります.

まとめ

本稿では,連続時間の積分器から出発し,離散時間での定義,さらにスイッチトキャパシタ(SC)回路による実装までを一貫して整理しました.離散時間における積分は総和として定義され,「電荷の累積」によって実装できることをまとめました.

ポイントを振り返ると,次のとおりです:

- 代表的な連続時間積分器は RC + オペアンプで構成される.

→抵抗が電圧を電流に変換し,容量が電流を積分する. - 離散時間では積分は総和となり,2種類の定義が存在する.

遅延付き\(H[z]=\frac{C}{C_F}\frac{z^{-1}}{1-z^{-1}}\)

遅延なし\(H[z]=-\frac{C}{C_F}\frac{1}{1-z^{-1}}/) - 分子の z^{-1} の有無が,1サンプル遅延の有無を決定する.

- SC積分器では,サンプリング容量が電荷を運び,フィードバック容量 \(C_F\) が電荷を保持・累積することで積分の振る舞いが成り立つ.

- SC回路は時間平均的にR_{eq}=\frac{T}{C}の等価抵抗として振る舞い,連続時間RC積分器と対応する.

以上,積分器の基礎についてまとめました.今後登場する複雑な構成の積分器も基礎の理解が深まっていれば,基本要素に分解できるようになります.次回は演習として,与えられた伝達関数から回路構成を導く方法を解説したいと思います.

以上です.最後まで読んでいただきありがとうございました.

雑記:今年もISSCCが盛り上がりましたね.ADC 関連の論文に関しては日本からの採択もあり,内容もとても興味深いものでした.このブログで論文レベルの記事を解説するには,まだまだ時がかかりそうですが,地道に自分のペースで進めていければと思っています.引き続き,お付き合いください.

参考文献

本記事はあくまで筆者の勉強備忘録のため,より正確に理解したい,さらに深く理解したい場合は下記をご参照ください.

- IIT Kanpur: https://www.iitk.ac.in

- SSCD Lab: https://iitk.ac.in/sscd

- 講義動画(YouTube): https://youtu.be/cI7bYpW7EvE?si=uhuL8tSMJan23LHf

- 『アナログ/デジタル変換入門 ― 原理と回路実装 ―』 和保孝夫(監)/コロナ社

- 『ΔΣ型アナログ/デジタル変換器入門 第2版』 和保孝夫・安田彰(監訳)/丸善出版

- 『アナログCMOS集積回路の設計 応用編』Behzad Razavi(著),黒田忠弘(監訳)/丸善出版

ー 第12章 スイッチトキャパシタ回路 ー - 『CMOSアナログ回路入門』 谷口研二(著)/CQ出版社

ー 第15章 スイッチト・キャパシタ ー

(ADCの基礎を一通り確認する目的で,最初の一冊として取り組みやすい内容です.)

(筆者が所持しているのは第 1 版ですが,こちらも分かりやすくておすすめです.)

スイッチトキャパシタについては,下記2冊が分かりやすいです.

(こちらの書籍では,積分器の遅延あり/なしをクロール型/バタフライ型と表記しています.)