本記事は,アナログ・デジタル変換器(ADC)を題材に,筆者自身の理解を深める目的で整理している「ADC入門シリーズ」の一部です.シリーズ全体の方針や位置づけについては,以下の記事をご覧ください.

はじめに

前回までの記事では,nMOS スイッチと pMOS スイッチ,そしてそれらを組み合わせた CMOS スイッチについて学習しました.CMOS スイッチは \(0〜V_{DD}\) の広いレンジで動作できる点が大きな利点ですが,それでもなお オン抵抗の非線形性 という課題は解消されません.

本稿では,この非線形性を大幅に改善できる手法としてゲート・ブートストラップスイッチを取り上げます.まず最初に「非線形の原因」を明確にし,続いて「どのような対策が有効か」,そして「それをどのように回路として実装するか」という流れで丁寧に整理していきます.

ADC のサンプリング回路において,サンプリングスイッチの線形性(linearity)は変換精度を左右する非常に重要な要素です.本稿を通じて,その改善手法について一緒に理解を深めていきましょう.

スイッチの非線形性の原因と対策

前回の記事の復習になります.ADC のサンプリングステージでよく用いられる nMOS スイッチは,そのままでは 非線形性(nonlinearity) を避けられません.その理由は,nMOS のオン抵抗が \(V_{GS}\) に強く依存しているためです.

\(R_{\text{on}} \propto \frac{1}{\mu C_{\text{ox}} (W/L)\,(V_{GS}-V_{TH})}\)

サンプリング中,ソース電圧は入力信号 \(V_{\text{in}}\) を追従するため,\(V_{GS} = V_{G} – V_{\text{in}}\) となり,入力電圧が大きくなるほど \(V_{GS}\) は小さくなります.結果としてオン抵抗は増加し,スイッチの電圧転送特性は非線形となります.

こうした非線形性は THD,SFDR,さらには SNDR といった ADC の主要性能指標に影響するため,サンプリングスイッチにおいて最初に対処すべき重要な課題です.

この非線形性に対する,もっとも直接的で強力な対策は \(V_{GS}\) を一定にすることです.しかも,より高い線形性を確保するには,できるだけ大きい一定値が望ましく,\(V_{GS} = V_{DD}\)を維持できれば,理想的なスイッチ動作が得られます.このときゲート電圧は次のようになります.

\(V_{G} = V_{\text{in}} + V_{DD}\)

上式から分かるように,「入力に対して常に \(V_{DD}\)だけ高いゲート電圧」が得られれば,入力がどのように変動してもオン抵抗を一定に保つことができます.

この条件を満たす最もシンプルなイメージは,「入力端とゲートの間に \(V_{DD}\) を加える」ことです.もちろん,\(V_{DD}\) の電池をスイッチの数だけ用意することは現実的ではありませんが,やりたいことはまさにこの動作です.また,スイッチを OFF にしたい場合は単純で,ゲートを 0 に落としておくだけで問題ありません.

以上が,非線形性の要因と,それに対する理想的な対策の概要です.しかし,毎サイクル「\(V_{\text{in}} + V_{DD}\)」を生成するのは一工夫が必要です.ここで重要な役割を果たすのが,次章で説明する 電荷保持素子としての容量(コンデンサ) です.

容量(コンデンサ)による実装

\(V_{\text{in}} + V_{DD}\) をオンチップで生成する実質的な手法が,ブートストラップ方式(bootstrap) です.

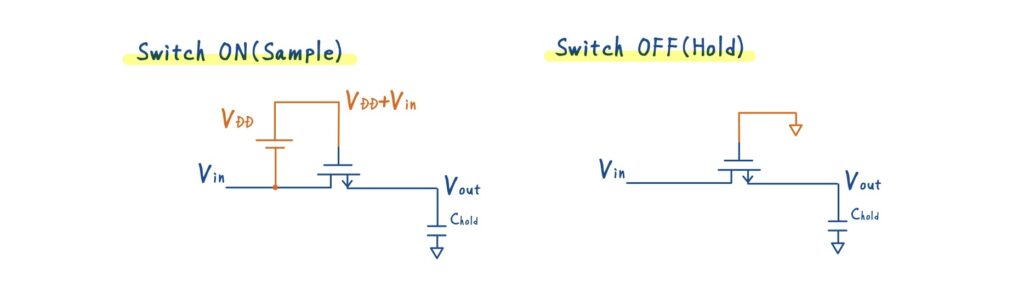

容量は「一度充電すると一定時間は電圧源のように振る舞う」という特性をもちます.この性質を利用し,あらかじめブートストラップ容量を \(V_{DD}\) まで充電しておき,必要なタイミングでその電圧をゲートに転送する,というのがブートストラップの基本的な考え方です.

ただし,一度充電しただけでは,リーク電流や寄生要領によって電圧は徐々に低下していきます.そのため容量は定期的にリフレッシュ(再充電)する必要があります.この再充電は スイッチ OFF 時 に行えばよく,動作は次のように整理できます.

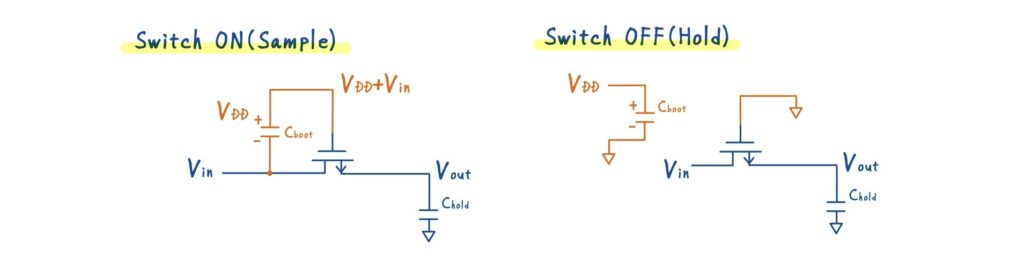

● ホールドモード スイッチ OFF(\(\phi = 0\))

- ブートストラップ容量 \(C_{\text{boot}}\) を \(V_{DD}\) に充電する.

- 同時に nMOS のゲートは GND に落とし,確実に OFF 状態を保つ.

● サンプルモード スイッチ ON(\(\phi = 1\))

- 充電済みの \(C_{\text{boot}}\) を nMOS のゲートに接続する.

- 容量電圧がソース側の \(V_{\text{in}}\) より持ち上げられることで,\(V_{G} = V_{\text{in}} + V_{DD}\) となり,結果として \(V_{GS} = V_{DD}\) を維持できる.

このように,容量によってゲート電圧を入力信号とともに押し上げる(bootstrap)ことで,nMOS スイッチのオン抵抗をほぼ一定に保つことができます.ブートストラップ方式が「非線形性の改善に非常に有効」とされる理由はここにあります.

注意点として,\(V_{\text{in}}\) が大きい場合,ゲート電圧が最大で約 \(2\,V_{DD}\) 程度まで上昇する可能性があります.このため,素子の耐圧設計 や,ブートストラップに伴う 誤導通の抑制 といった点が実装上の重要な設計項目になります.

ゲート・ブートストラップ・スイッチ(G.B.S)の構成

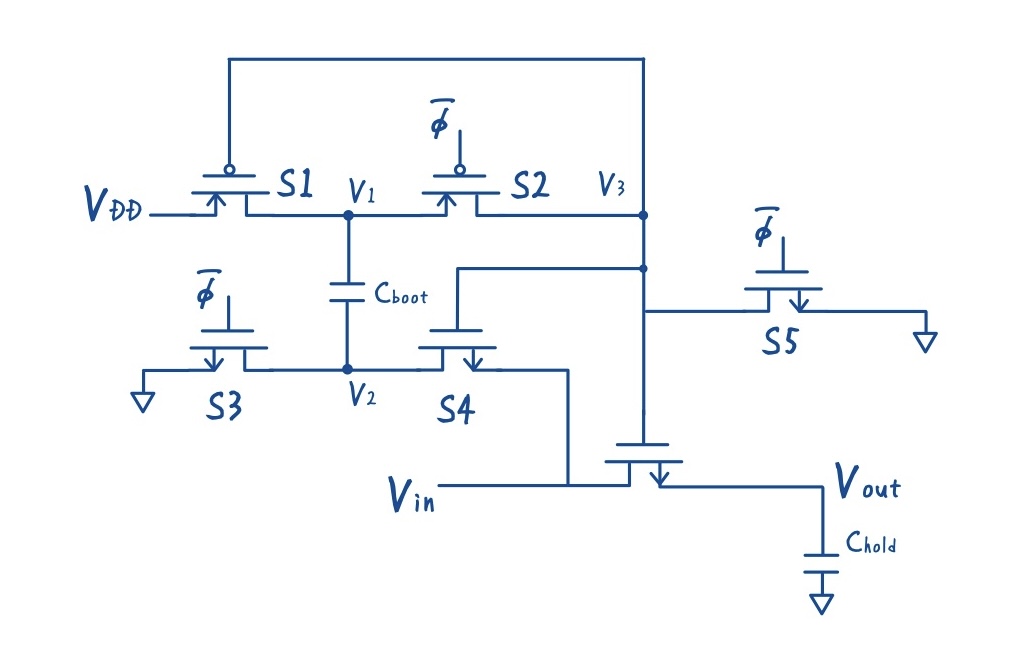

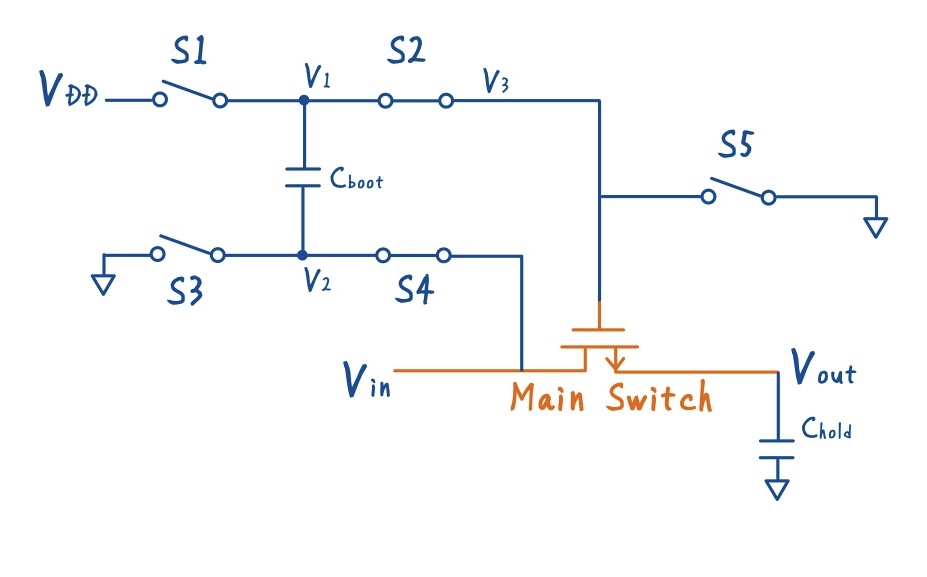

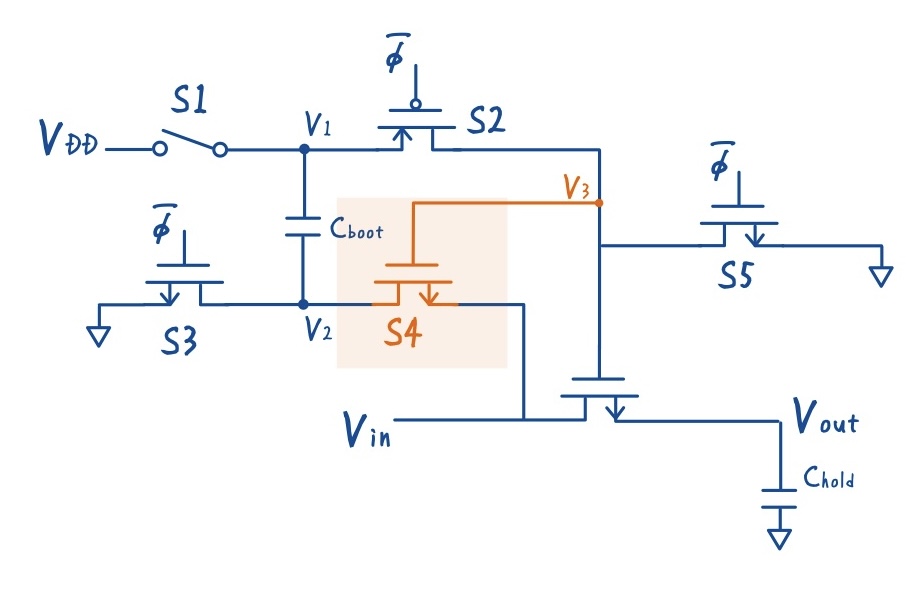

ブートストラップ方式を実現するためには,単に nMOS と容量を並べるだけでは不十分です.ブートストラップ容量を ON/OFF の各フェーズで適切なノードへ接続・切り離しする制御 が必要であり,そのためには複数の補助スイッチを組み合わせた構成が求められます.代表的な構成は次のとおりです.

- メイン nMOS:サンプリング本体を担う

- S1:ブートストラップ容量を \(V_{DD}\) に充電するスイッチ

- S2:充電された電圧をゲート側へ転送するスイッチ

- S3:ブートストラップ容量のもう一端を GND へ接続するスイッチ

- S4:\(V_{\text{in}}\) とゲート駆動を同期させるためのスイッチ

- S5:ゲートノードを GND へ放電し,リセットするスイッチ

- \(C_{\text{boot}}\):ゲートを \(V_{\text{in}} + V_{DD}\) に押し上げるための容量(ブートストラップ容量)

これらのスイッチ群は \(\phi\)/\(\overline{\phi}\) のクロックで制御され,「OFF 期間には容量を充電し,ON 期間にだけ \(V_{\text{in}} + V_{DD}\) を生成する」という一連の動作サイクルを成立させます.

G.B.Sのトランジスタレベルの実装

前章では,ゲート・ブートストラップ・スイッチ(G.B.S)を構成する補助スイッチ群の役割を整理しました.ここでは,それらを現実的なトランジスタ構成へと落とし込みます.各スイッチの動作を理解しやすくするため,本稿では図中のノード電位を \(V_1 \sim V_3\) のように定義して議論を進めます.(解説の分かりやすさを優先して,スイッチ番号の順番とは対応していない点に注意してください.)

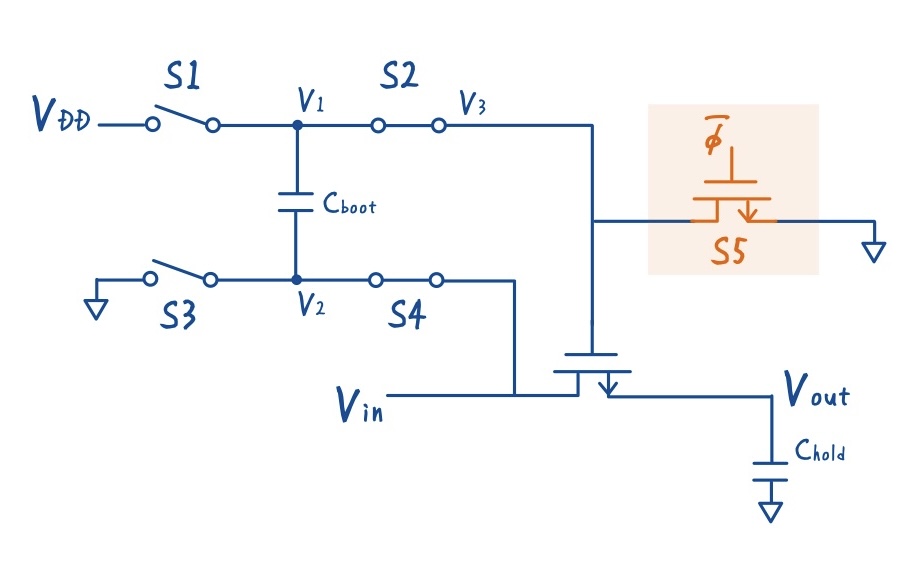

S5 (ゲートノードのリセット)

最も組み立てやすいのは S5 です.S5 は,ホールド時(\(\phi = 0\))にゲートノード \(V_3\) を GND へ落とす役割を持ちます.

・構成:nMOS(プルダウンの定石)

・制御:サンプル時(\(\phi = 1\))は切り離し → \(\overline{\phi}\) で制御

リセット動作は G.B.S の安定動作に不可欠であり,S5 はその最初の要となるスイッチです.

S3 (ブートストラップ容量の下側制御)

次に考えやすいのは S3 です.こちらも GND へのプルダウンであり,役割は「ブートストラップ容量 \(C_{\text{boot}}\) のもう一端を OFF 時に GND へ固定する」ことです.

- 構成:nMOS

- 制御:S5 と同様に,\(\overline{\phi}\)

S3 と S5 は用途は異なりますが,どちらも「OFF フェーズで確実にノードを 0 V に落とす」という定番構成です.

S2(\(V_1–V_3\) のハイレベル電圧転送)

S2 は,サンプル時(\(\phi = 1\))に \(V_1\) と \(V_3\) を接続してブートストラップ電圧をゲートへ転送するスイッチです.\(V_1\),\(V_3\) の電圧範囲は \(V_{DD} \sim V_{DD} + V_{\text{in}}\) のように \(V_{DD}\) を超えるHigh レベル信号 を扱います.このため,High レベルの信号を通すには pMOS を使うのが自然です.

- 構成:pMOS

- 制御:pMOS を ON にするため,サンプル時はゲートを Low にしたい → \(\overline{\phi}\)

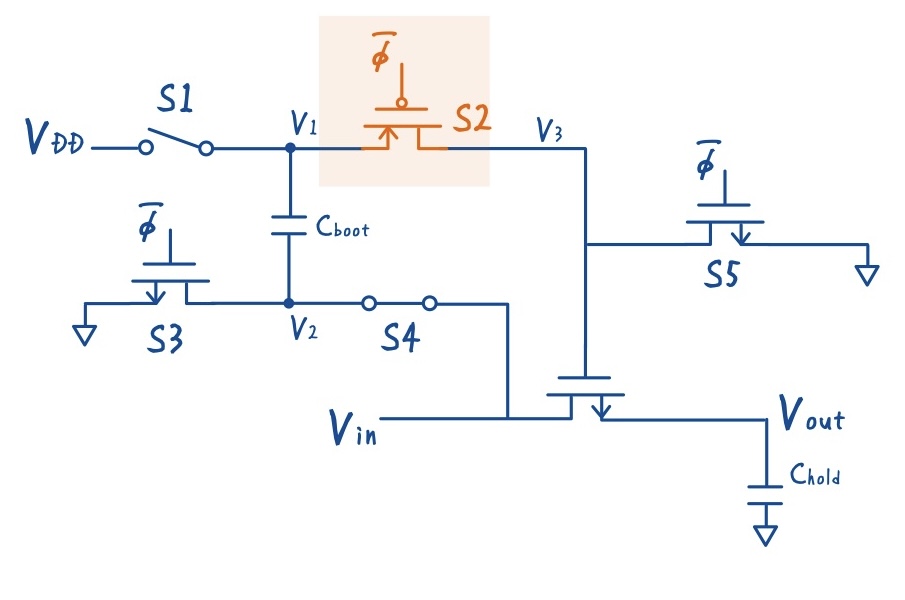

S4

S4 はnMOS での構成を考えますが,ゲート電圧の与え方が他のスイッチ等と違い工夫が必要です.前提として,サンプル時にソース側は \(V_{\text{in}}\) まで持ち上がります.特に最大入力時は\(V_{\text{in}} \approx V_{DD}\)となり得ます.このとき,ゲート電圧が単なる \(V_{DD}\) では\(V_{GS} = V_{DD} – V_{DD} = 0\)となり,nMOS は オンになれません.

そのため,必要なのは \(V_G \ge V_{\text{in}} + V_{TH}\)のような \(V_{\text{in}}\) より高いゲート電圧 です.そこで登場するのが,\(V_3\) のノードの電圧です.ちょうどこの \(V_3\) が都合の良い動作をするため,この電圧をゲート駆動用として利用します.

\(V_3 = V_{\text{in}} + V_{DD}\)

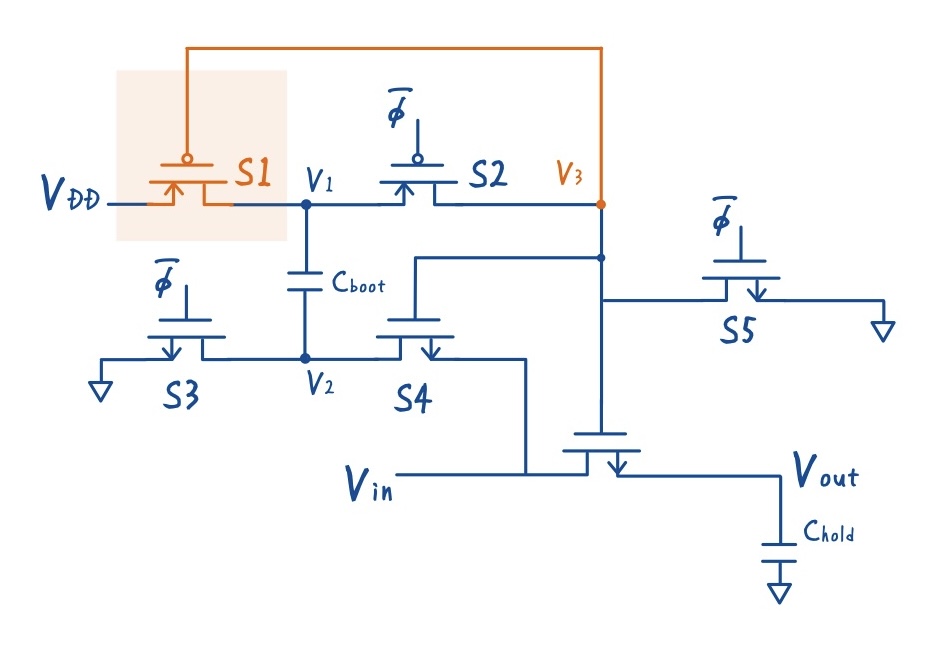

S1

最後にS1 です.S1 はブートストラップ容量を \(V_{DD}\) に充電するスイッチであり,高電位側の信号を扱うため pMOS が適切です.しかし,S1 のポイントは「オフ時に誤導通しない設計」です.サンプル時には \(V_1\) が最大で約 \(2V_{DD}\) に達することがあります.もしゲート制御を単に \(V_{DD}\) としてしまうと,下記の状態になってしまいます.

- pMOS のゲート:\(V_{DD}\)

- ドレインまたはソース:\(2V_{DD}\)

このような場合,ドレイン/ソース側がより高いため pMOS がオンしてしまう(ソースが入れ替わる)問題が起きます.そこで,S4 と同様の発想で ゲートを \(V_3\) へ接続し,これにより「入力電圧に追従したゲート電圧」が得られ,オフ時にも安全に切り離される構成にします.

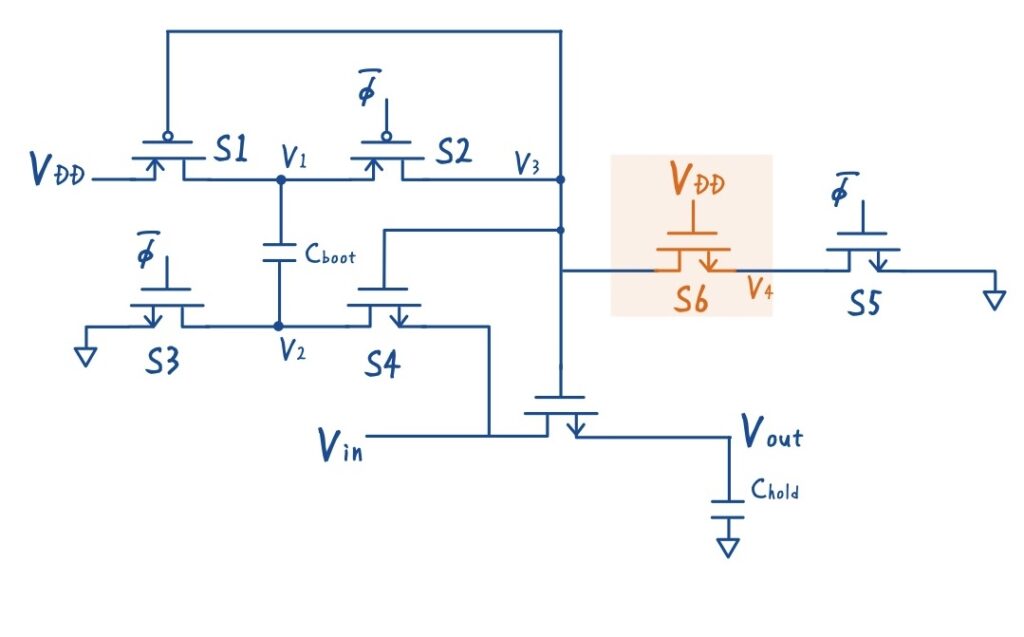

S6

S6 は必須ではありませんが,現実の IC ではよく挿入される保護スイッチです.理由としては \(V_3\) が最大で \(2V_{DD}\) まで上昇した場合,S5 のドレイン‐ソース間に \(2V_{DD}\) の電圧が印加されてしまいます.すると,トランジスタの耐圧によっては破壊やリーク増加のリスクが発生してしまいます.そのため,S5 の前段に 常時 ON の nMOS(S6)を直列に配置します.これにより,S6 のゲートは常に \(V_{DD}\) ですから,\(V_4\)(S5 との間のノード)が上昇すると,S6 の \(V_{GS}\) が低下→S6 が自然に OFF 方向へ寄り,耐圧を分散してくれるという 保護ダイオード的な効果 を発揮します.ハイレベル電圧が重畳するブートストラップ回路ではよく使われる技法で,覚えておくと応用範囲が広いです.

以上で各スイッチの構成が揃いました.ブートストラップ方式の設計では,以下のような注意が必要です.

- 補助スイッチのオン抵抗が大きすぎると容量の充電時間が増える.

- 時定数 RC が立ち上がりを支配する.

- 容量値とスイッチサイズの最適化が必須.

- \(V_DD\) を超えるノードが存在するため,MOS の向き(ソース/ドレイン)やボディ接続の扱いが非常に重要.

結局のところ,この手の回路は 「容量の充放電を,必要時間内にきちんと終わらせる」 という時定数との戦いに尽きますね.

スイッチの使い分け

講義の最後でも触れられていたように,スイッチの選択は 「扱う信号の特性」 を基準にすると整理しやすくなります.これまでに学んだ 4 種類のスイッチについて,特徴と適した用途を簡単にまとめておきます.複雑な回路でない限り,これらのスイッチを適切に使い分けるだけで多くの場面をカバーできます.それぞれの性質をよく理解しておくことが大切です.

| スイッチ | 特徴 | 適用途 |

|---|---|---|

| nMOS | Low レベル域で安定 低オン抵抗 | Low レベル信号の保持 |

| pMOS | High レベル域(\(V_{DD}\) 付近)で安定 | High レベル信号の保持 |

| CMOS(TG) | \(0〜V_{DD}\) 全域で電圧保持が可能 | 一般的な保持用途 |

| G.B.S | 高い線形性を実現 消費電力・回路規模増 | 時間変化する信号のサンプリング |

特に,今回扱った G.B.S(ゲート・ブートストラップ・スイッチ) は,サンプリングフェーズのように時間変化する信号に対して真価を発揮します.反対に,保持(Hold)だけが目的であれば,G.B.S を使う必要はありません.通常の CMOS TG のほうがシンプルで堅実ですし,面積・消費電力・設計負荷の面でも合理的です.

保持にしか使わない場面で G.B.S を入れてしまうのはオーバースペックであり,講義中の例えを借りればまさに「蚊に AK-47」ですね.笑ってしまう表現ですが,過剰設計の本質をよく捉えていると思います.

補足:G.B.Sのメリット(電源の低電圧化)

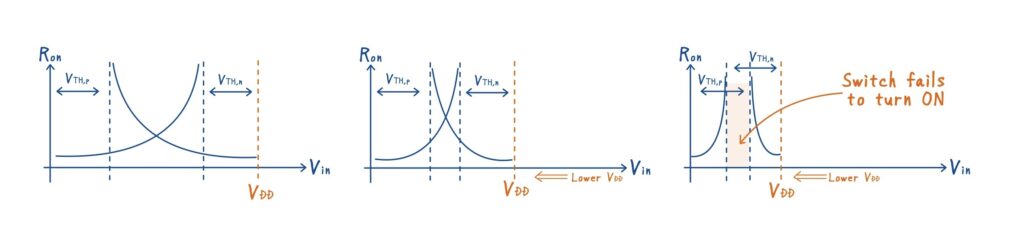

これまで G.B.S のメリットを「オン抵抗の線形性」という切り口で説明してきましたが,実はもう一つ重要なメリットがあります.それが,低い電源電圧でも動作しやすいという点です.この背景を理解するために,まず CMOS トランスミッションゲート(T.G)が低電圧を苦手とする理由を簡潔にまとめます.

T.G は nMOS と pMOS を並列に組み合わせたスイッチで,十分な \(V_{DD}\) があるときは \(0〜V_{DD}\) の広いスイングを扱える便利な構成です.しかし,電源電圧を下げていくと構造的な限界が現れます.

\(V_{DD}\) を下げると,nMOS の「High が通りにくい帯域」と,pMOS の「Low が通りにくい帯域」が互いに中央へ向かって広がり,最終的には T.G として扱えない電圧帯が生じます.つまり,T.G は基本的に十分な電源ヘッドルーム(\(V_{DD} ≥ V_{TH,n} + V_{TH,p}\))を前提としたスイッチ なのです.

一方で,G.B.S は本記事で説明したように,ON 時には\(V_{GS} = V_{DD}\) が常に成立する構造のため,\(V_{DD} ≥ V_{TH,n}\) であれば動作します.

まとめると,スイッチを動作させるためのヘッドルーム条件は下記のようになり,G.B.S のほうが低い \(V_{DD}\) でも動作可能であることがわかります.

- T.G: \(V_{DD} ≥ V_{TH,n} + V_{TH,p}\)

- G.B.S: \(V_{DD} ≥ V_{TH,n}\)

まとめ

本稿では,nMOS スイッチが本質的に抱えるオン抵抗の非線形性を出発点とし,その問題をどのように克服できるのかを丁寧に追いました.ゲート電圧を入力信号に応じて持ち上げることで \(V_{GS}=V_{DD}\)を維持し,高い線形性を実現する ゲート・ブートストラップスイッチ(G.B.S) の原理と構成を詳しく学びました.サンプリングスイッチの非線形性は ADC の精度に直結するため,そのメカニズムを理解しておくことは非常に重要です.

ポイントを振り返ると次のとおりです:

- nMOS スイッチは \(V_{GS} = V_{G}-V_{\text{in}}\) に依存し,入力電圧が上がるほどオン抵抗が増大する.

→ これがスイッチ非線形性の根本原因. - 理想的には \(V_{GS}\) を一定値 \(V_{DD}\) に保つことで,オン抵抗を入力非依存にできる.

- ブートストラップ容量を用いることで,サンプリング時に \(V_{G} = V_{\text{in}} + V_{DD}\) を生成し,結果として常に \(V_{GS}=V_{DD}\) を達成できる.

- 実現には S1〜S5 の補助スイッチを適切に配置し,φ/φ̄ による充電・転送・リセットのサイクルを構成する必要がある.

- G.B.S は高線形なサンプリングが可能

- 一方で,充放電回路が増えるため,消費電力や回路規模が大きくなる点には注意が必要.

→ スイッチ選択は用途に応じたトレードオフで決まる.

以上です.今回は nMOS の非線形性を根本的に改善するアプローチとして,ゲート・ブートストラップスイッチの原理と実装方法を整理しました.

最後まで読んでいただきありがとうございました.

参考文献

本記事はあくまで筆者の勉強備忘録のため,より正確に理解したい,さらに深く理解したい場合は下記をご参照ください.

- IIT Kanpur: https://www.iitk.ac.in

- SSCD Lab: https://iitk.ac.in/sscd

- 講義動画(YouTube): https://youtu.be/cI7bYpW7EvE?si=uhuL8tSMJan23LHf

- 『アナログ/デジタル変換入門 ― 原理と回路実装 ―』 和保孝夫(監)/コロナ社

- 『ΔΣ型アナログ/デジタル変換器入門 第2版』 和保孝夫・安田彰(監訳)/丸善出版